東北大学技術

整理番号:T05-100

半導体記憶装置

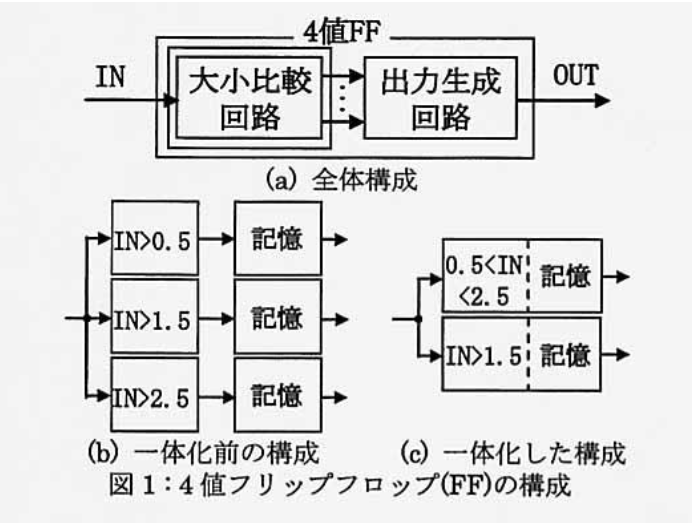

多値差動ロジックを用いたロジック回路、記憶回路、複合回路

概要

従来のCMOS回路を用いたLSIにおいては、クロック数の上昇に伴い、消費電力の増大が指摘されている。電流モードによる回路技術は、600MHz程度の周波数以上においては、CMOSよりも消費電力の低減が図ることができる。

本発明は、多値作動ロジックに基づくフリップフロップの構成により、静的な記憶保持回路を提供するものである。 これまでの研究の結果で、多値差動ロジックを用いて、ロジック回路、記憶回路、複合回路の構成が可能となった。

効果・応用例

●応用例

• 多値差動ロジックを用いたロジック回路、記憶回路、複合回路

知的財産データ

知財関連番号 : 特開2007/023727A1

発明者 : 羽生 貴弘

技術キーワード: エレクトロニクス、情報・通信(ハードウエア)