東北大学技術

整理番号:T06-167

半導体集積回路装置及びその製造方法

半導体チップの歩留まりの改善及び設計マージンの緩和

概要

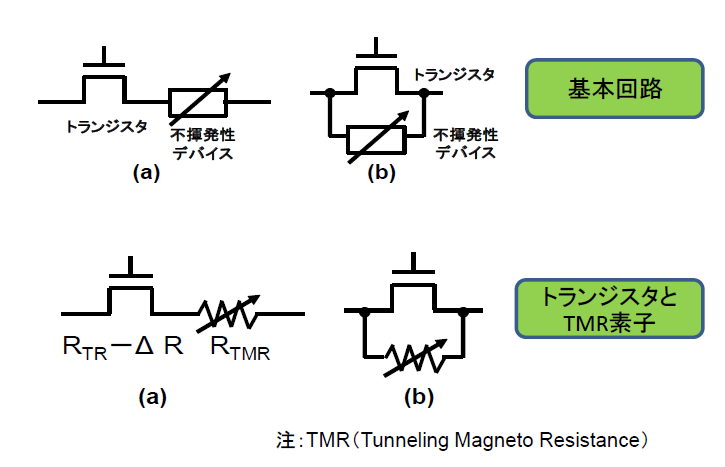

ナノメートル世代の半導体チップにおいては、チップ内の同一形状のトランジスタであっても、製造過程のばらつきにより特性が異なってくる。そのため、良品チップの歩留りが低下したり、良品チップでも性能が劣化するといった問題が生じる。 本発明は、トランジスタの特性ばらつきによる動作不良や性能劣化を製造後に検出し、トランジスタに付加された補正素子により特性の改善を行い、その部分、または回路全体の動作を良品レベルに引き上げ、歩留りおよび性能を向上させようというものである。

基本回路構成

効果

半導体チップのトランジスタの特性ばらつきを製造後に補正することで歩留りおよび性能を改善可能である。さらに製造プロセス制約や設計マージン制約等が緩和され、より高性能な半導体チップを制約にとらわれずに回路設計が可能となる。

知的財産データ

知財関連番号 : 2008-235621

発明者 : 羽生 貴弘、望月 明、白濱 弘勝、三浦 成友、大野 英男

技術キーワード: エレクトロニクス、情報・通信(ハードウエア)